# High Gain Broadband CMOS Low Noise Amplifier Using Π-Matching Technique

# Jitendra Gupta

M. Tech. Scholar

Department of Electronics and Communication Engineering Technocrats Institute Of Technology, Bhopal er.jkgupta.nri@gmail.com

# Prof. Shivraj Singh

Assistant Professor

Department of Electronics and Communication Engineering Technocrats Institute Of Technology, Bhopal 86.shivraj@gmail.com

**Abstract-** A Low Noise Amplifier is presented with high gain and low noise using 0.18 SOI CMOS technology. The linearity issue in Broadband Radio Frequency front end is introduced. MOSFET non linearity characteristics cause linearity problems in the RF front end system. To overcome linearity problem and achieve less reflection in the circuit we use HEMT. The Dual Loop Feedbacks reverse gain and reverse isolation of LNA at 1GHz to 10GHz frequency with small dc blocking capacitor is used. In addition, - Matching Network is used to match a high impedance source to lower value and its vice-versa. In this design an Inductor Feedback is used to achieve good Input Impedance match and a low noise figure. This designed Low Noise Amplifier achieves high gain (S12) of -173.2 dB, a noise figure in the range (3.1dB to 2.1dB) over the frequency range 1GHz to 10 GHz and power dissipation of 1.913 pW. All these mesurement can be taken from LT-Spice Simulator.

Keywords- CMOS, Matching network, peaking inductor, inductive feedback, HEMT, Dual loop feedback, Electro static discharge.

# I. INTRODUCTION

The Low Noise Amplifier is the most critical section of a receiver front end in term of receiver performance. With different configurations many circuits have been proposed for Low Noise Amplifier in different applications. Circuit must be designed and optimized after choosing proper Low Noise Amplifier. Various types of techniques have been proposed for Low Noise Amplifier design and optimizations. In this section an overview of available Low Noise Amplifier circuits and design and optimization techniques will be described. We have seen the emergence of numerous new radio applications and technologies. The ever increasing demand for larger wireless transfer capacity tends to saturate the low GHz bands of current in use wireless standards such as wireless fidelity, Bluetooth, Ultra Wideband live global projection system, Wi-Max, satellite mobile phone etc. The commonly accepted solution to over congestion problem is to resort to the 30GHz band where bandwidth is abundantly available. The development has been go fast and field of new innovations is wide. The development of wireless systems has diverged, antenna and radar system also with the trend now being to offer different data rates. High data rates and wide bandwidths are provided to consumers to transfer larger volume of data in smaller time. On the other hand, a class of applications exists that do not require high speed or bandwidth, but still gain benefit from wireless connection.

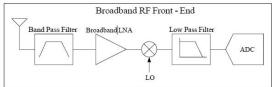

A Low Noise Amplifier will process a broadband signal to cover a very wide frequency band in the system. In broadband radio frequency front end a band pass filter eliminates un-useful signals outside the frequency band. Anyhow, interferers may exist inside the band pass filter.

Figure 1: Broadband RF front end

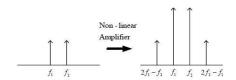

The main point of discussion of a broadband Low Noise Amplifier is its linearity. If we have a non linear amplifier, the third order inter-modulation distortion of non linear amplifier usually falls into the original signal band.

Figure 2: IM3 distortion non linear amplifier

BPF eliminate interferers and prevents a Low Noise Amplifier from producing a large power image signal, Interferer third intermodulation distortion, close to the original signal, S1. Thus, the original signal can be retained in spite of the image signal. Anyhow, this scenario desperately changes in the case of a broadband Low Noise Amplifier.

Figure 3: Signal processing in broadband LNA

A band pass filter is a broadband. Thus, interferers IM3 existing near the original signal and are not suppressed as shown in Figure 3. As a result of cross terms of non linear devices, these interferers IM3 create an image signal, near the original signal, S1. A Low Noise Amplifier needs to be linear to minimize the power of the image signal. If a Low Noise Amplifier is not linear enough, the image signal power may be similar to that of the original signal which would make the original signal identical. In other way, the Minimum Signal of the system that can be detectable is dominated by the image signal produced due to cross terms present in the non linear devices. During this situation, lowering Noise Figure does not help to improve the Minimum detectable Signal performance of the system. If the last stage of a radio frequency front end is normally considered the most important in the linearity performance, linearity of a Low Noise Amplifier and a Mixer in a broadband multi-standard radio frequency front end are also significant.

# II. DUAL LOOP FEEDBACK TECHNIQUE

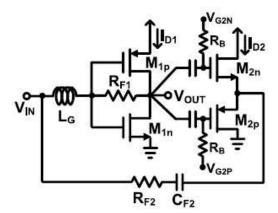

As shown in figure the dual-loop feedback Low Noise Amplifier and its small signal equivalent circuit model. All of the building blocks of the proposed Low Noise Amplifier, which is composed of an inverter-based resistive feedback amplifier and a complementary source follower, utilize the complementary operation of NMOS and PMOS to increase the trans-conductance by current reuse and to reduce the second order nonlinearity.

Figure 4: Dual Loop Feedback LNA

The dual loop feedback can be expressed as the expression of their input impedance and power gain as shown below-

$$\begin{split} Z_{in} = & \frac{1}{j\omega \left(C_{gs.m1} + C_{M1}\right)} \|R_{M1}\| \frac{R_{M1} + \frac{1}{j\omega C_{F2}} + \frac{1}{g_{m.m2}}}{1 + g_{m.m2} Z_L} \end{split}$$

power gain =

$$20 \log \left(\frac{_{2}Z_{in}}{_{R_S + Z_{in}}} g_{m.m1} Z_L\right)$$

# III. GATE PEAKING INDUCTOR TECHNIQUE

One major drawback of the complete dual-loop feedback Low Noise Amplifier is the bandwidth reduction due to large input and load capacitances at the input and output nodes. In particular, the Miller capacitance at the input node severely degrades the bandwidth of the complete Low Noise Amplifier as compared to that of the conventional source follower feedback Low Noise Amplifier. In order to enhance the bandwidth of the Low Noise Amplifier, the series peaking inductor  $L_G$  is placed inside the feedback loop at the gate of the input transistor. Compared to the inductor shunt peaking technique in which an inductor is added in series with the load resistor, the inductor series peaking technique only requires much smaller inductor in order to achieve a similar bandwidth extension  $Z_{IN}$  and  $S_{21}$  of the complete Low Noise Amplifier with the series peaking inductor  $L_G$  are modified as follows.

$$\begin{split} Z_{IN} \approx \left\{ &j\omega L_G + \left( \frac{1}{j\omega \left( C_{gs.m1} + C_{M1} \right)} \| \ R_{M1} \right) \right\} \\ &\left\| \frac{R_{F2} + \frac{1}{(j\omega C_{F2})} + \frac{1}{gm.\,m2}}{1 + \beta_{gm.m1} Z_L} \right. \end{split}$$

Where,

$$\beta \approx \frac{\frac{1}{L_{G(C_{gs.m1} + C_{M1})}}}{\left(\frac{1}{L_{G(C_{gs.m1} + C_{M1})}} - \omega^{2}\right) + j\frac{1}{\left(C_{gs.m1} + C_{M1}\right)R_{M1}}\omega}$$

And

$$S_{21} \approx 20 log \left[ \frac{2Z_{in}}{R_s + Z_{in}} \beta_{gm.m1} Z_L \right]$$

The peaking frequency is approximately given by

$$\omega_{peak} \approx \frac{1}{L_{G(C_{gs.m1} + C_{M1})}}$$

# IV. II-MATCHING TECHNIQUE

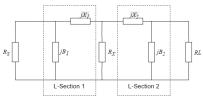

A  $\Pi$ -Section Matching Network consists of three elements arranged as shown in figure. The  $\Pi$  - Section can be considered as consisting of a type 2 L- section followed by a type 1 L-section in cascade as shown in fig. where the central element, X, has been split into two reactive elements of the same type, that is, X = X1 + X2.

Figure 5: Π-Matching Technique

We also postulate an "invisible" load resistance,  $R_1$  Interposed between the two L sub networks. The purpose of L- section 2 is to match  $R_1$  to the load. The individual L- section can be designed according to the principles set out in the previous section. Provided we know the value of  $R_1$  which is the value of  $R_1$  can be chosen arbitrarily. But it should be smaller than both  $R_S$  and  $R_L$ .

$$Q_{1.1} = \sqrt{\left(\frac{R_S}{R_x} - 1\right)}$$

Apply the same logic, the loaded Q of L- network 2, which matches  $R_x$  to  $R_L$  (which is larger than  $R_x$ ), is given by.

$$Q_{1.2} = \sqrt{\left(\frac{R_L}{R_x} - 1\right)}$$

Since the loaded Q of the overall circuit is determined by the branch of the circuit having the highest loaded Q-value, we can write the overall Q of the circuit in Figure  $Q_{\pi}$ , as

$$Q_\pi = \sqrt{\frac{R_{\rm high}}{R_x} - 1}$$

# V. HIGH ELECTRON MOBILITY TRANSISTOR

Available online @ www.ijntse.com

An important aspect of High Electron Mobility Transistor is used as an important aspect that band discontinuities across the valence band and conduction bands can be modified separately. This will provides the type of carriers in and out of the device to be controlled easily. As High Electron Mobility Transistor needs electrons to be the majority carriers, doping can be applied in one material to make the conduction band discontinuity as smaller as possible, and keeping the same valence band discontinuity. This diffusion of the majority carriers results in to the accumulation of electrons along with the boundary of the two regions. This type of electron accumulation results in very high current, and this type of electron accumulation are known as two dimensional electron gases. High Electron Mobility Transistor is used in application where low noise and high gain at high frequencies are required. High Electron Mobility Transistor have shown power gain to frequencies greater than 1 THz and current gain to frequencies greater than 600 GHz.

# VI. INDUCTIVE FEEDBACK

In our design work in the first stage transistor for together achieving high linearity and wideband characteristic an inductive shunt feedback circuit is used in between drain and gate. The equation for input impedance is deduced analytically to get the high and low input impedance matching frequencies of the pass band of interest. Because of the shunt inductor located in the feedback loop the linearity has been improved gradually and overcome the third order harmonics at the output port. The LNA is designed at 1.3 GHz for attaining narrow band gain especially targeting wind profiling radars. The LNA is designed using P-HEMT device with a dc bias of 3 V and drain current of 60 mA.

#### VII. IMPLIMENTATION OF DESIGN

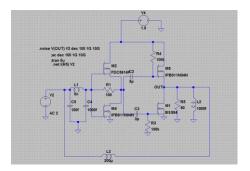

Figure shows the implemented design of our proposed work in which we use three technique such as  $\pi$ -matching network, high electron mobility transistor, and an inductive feedback.

Figure 6: Implementation of proposed design

#### VIII. RESULT PARAMETER

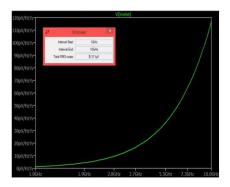

# • Input Noise (IN)

The input of the design is given in terms of input noise. In this figure 7 X –axis shows the frequency range from 1GHz up to 10 GHz and the Y- axis shows the noise figure in  $pV/\sqrt{Hz}$ .

Figure 7: Shows the Input Noise design (GHz)

This is output noise at different frequency-Input noise at  $1 \text{GHz} = 0.25 \text{ pV}/\sqrt{\text{Hz}}$ Input noise at  $10 \text{GHz} = 115 \text{pV}/\sqrt{\text{Hz}}$ . Average RMS input noise =  $5.311\mu V$

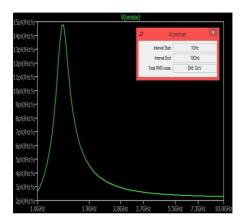

# • Output Noise (ON)

The output of the design is given in terms of output noise (ON) as shown in figure 8. In this figure 8 X –axis shows the frequency range from 1GHz up to 10 GHz and the Y- axis shows the noise figure in  $pV/\sqrt{Hz}$ .

Figure 8: Shows the Output Noise design (GHz)

This is output noise at different frequency-Output noise at  $1 \text{GHz} = 2.6 \text{pV}/\sqrt{\text{Hz}}$ Output noise at  $1.5 \text{GHz} = 14.9 \text{pV}/\sqrt{\text{Hz}}$ Output noise at  $10 \text{GHz} = 2.4 \text{pV}/\sqrt{\text{Hz}}$ Average RMS output noise = 345.12 nV

# • Noise figure (NF)

The noise figure is defined as the difference in decibels between the signal to noise ratio of output of actual receiver to the signal to noise ratio of input of ideal receiver with similar bandwidth and overall gain.

|        | Input | Output | Vin | Vout | NF       |

|--------|-------|--------|-----|------|----------|

|        | Noise | Noise  |     |      |          |

|        |       |        |     |      |          |

| 1GHz   | 1     | 2.6    | 2   | 4.3  | 1.65     |

| 2.5GHz | 5     | 3.6    | 2   | 1    | 3.16     |

|        |       |        |     |      |          |

| 4GHz   | 20    | 2.9    | 2   | 0.3  | 0.29     |

| 6.5GHz | 45    | 2.5    | 2   | 0.1  | 0.915    |

| 8GHz   | 70    | 2.3    | 2   | 0.05 | 2.3      |

| 10GHz  | 11.5  | 2.2    | 2   | 0    | infinity |

Table 1: Noise Figure at different frequency

The noise factor F of a system is represented as give below

$$F = \frac{SNR_{in}}{SNR_{out}}$$

Where,

SNRin = Signal to noise ratio of input SNRout = Signal to noise ratio of output.

The Signal to noise ratio quantities are voltage ratios and the noise figure is defined in terms of noise factor in dB.

$$NF = 10 \log_{10}(F)$$

$$= 10 \log_{10} \left(\frac{SNR_{in}}{SNR_{out}}\right)$$

$$= SNR_{in,dB} - SNR_{out,dB}$$

# S-Parameters

At Microwave frequencies and high radio frequency (RF), direct measurement of two port network parameters i.e. Y, Z or H-parameters is very difficult to calculate due to absence of equipment to calculate radio frequency (RF) or microwave frequency (MW) total current and voltage due to difficulty of obtaining perfect opens or shorts. Since active devices may be unstable at open/short conditions. In two port device there is a parameter with their element S11, S12, S21, and S22 parameter, where S11, and S22 are the forward and reverse reflection coefficients, with the opposite port terminated in Z0 (usually 50 ohms.) and S21 and S12 are the forward and reverse gains assuming a Z0 source and load (again usually 50 ohms).

$$b1 = S11a1 + S12 a2$$

$b2 = S21a1 + S22 a2$

S parameter-

$$s_{11} = \frac{b_1}{a_1} \bigg|_{a_2 = 0}$$

$$s_{21} = \frac{b_2}{a_1} \bigg|_{a_2 = 0}$$

$$s_{12} = \frac{b_1}{a_2} \bigg|_{a_1 = 0}$$

$$s_{22} = \frac{b_2}{a_2} \bigg|_{a_2 = 0}$$

S11 – input reflection coefficient with the output matched

S21 – forward transmission gain or loss

S12 – reverse transmission or isolation

S22- output reflection coefficient with the input matched

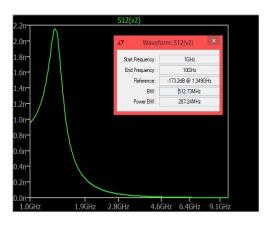

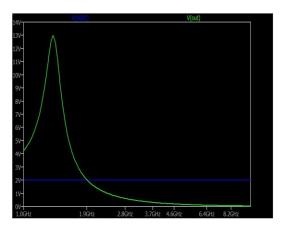

Figure 9: Shows the S12 parameter waveform

In the simulation of S- parameter which is given by S12 of design for 1 to 10 GHz frequency discuss in the figure 9. In this figure X-axis express the frequency range up to 10 GHz and Y-axis express the bandwidth of S-parameter in decibel (dB). S-parameters

describe the input-output relationship between in a design system. S-parameter is also known as the reflection parameter which obtained and generally S-parameter is said to be good enough below -10 dB.

S-parameter = <-19 dB S-parameter bandwidth = 1.5GHz

#### Gain

A Low Noise Amplifier without high-gain grants the signal to be affected by Low Noise Amplifier circuit noise. The Low Noise Amplifier must have high gain. The signal may become LNA gain also varies with operating frequency, like noise figures.

Figure 10: shows graph of power gain

# IX. CONCLUSION

In this design of a Low Noise Amplifier using  $\pi$ -matching network, HEMT, inductive feedback technique we draw various type of plot such as output noise, input noise, gain plot, s-parameter, using LT Spice software. These results obtained in the simulation and are optimized in the typical library. This Low Noise Amplifier is designed for the frequency applications ranges from 1GHz to 10GHz. A Noise Rejection Circuit is developed by using  $\Pi$ -Matching Network. To increase gain of LNA an inductor is used in feedback network. Based on this technique -11.9 dB noise figure and 283.5 MHz Gain bandwidth is obtained in frequency range of 1GHz to 10GHz. The amplifier present high gain with minimum noise figure (NF). The LNAs noise figure as well as power consumption has major impact in deciding the systems overall performance. Hence, the obtained LNA parameters after designing are utilized in the simulation of other different RF circuits.

### X. REFERENCES

- [1] Donggu Im, Member, IEEE, and In-Young Lee, Member, IEEE "A High IIP Broadband CMOS Low-Noise Amplifier With a Dual-Loop Feedback" 2016

- [2] Sumit Bagga, Member, IEEE, Andre L.Mansano, Student Member, IEEE, WouterA.erdijn, Fellow, IEEE, John R. Long, Member, IEEE, Koen Van Hartingsveldt, Member, IEEE, and Kathleen Philips, Member, IEEE "A Frequency-Selective Broadband Low-Noise Amplifier With Double-Loop Transformer Feedback" 2013

- [3] Jeong-Yeol Bae, Student Member, IEEE, Suna Kim, Student Member, IEEE, Hong-So in "A CMOS Wideband Highly Linear Low-Noise Amplifier for Digital TV Applications" 2013

- [4] Hong-Yeh Chang, Member IEEE, Chi-Hsien Lin, Yu-Cheng Liu, Student Member IEEE, Yeh-Liang Yeh, Student Member IEEE, Kevin Chen, and Szu-Hsien Wu "65-nm CMOS Dual-Gate Device for Band Broadband Low-Noise Amplifier and High-Accuracy Quadrature Voltage-Controlled Oscillator" 2013

- [5] Han-Chih Yeh, Student Member, IEEE, Sofiane Aloui, Chau-Ching Chiong, Member, IEEE, and Huei Wang, Fellow, IEEE "A Wide Gain Control Range-Band CMOS Variable-Gain Amplifier with Built-In Linearizer" 2013

- [6] Xiaohua Yu, Student Member, IEEE, and Nathan M. Neihart, Member, IEEE "Analysis and Design of a Reconfigurable Multimode Low-Noise Amplifier Utilizing a Multitap Transformer" 2013

- [7] Han-Chih Yeh, Student Member, IEEE, Chau-Ching Chiong, Student Member, IEEE, Sofiane Aloui, and Huei Wang, Fellow, IEEE "Analysis and Design of Millimeter-Wave Low-Voltage CMOS Cascade LNA With Magnetic Coupled Technique" 2012

- [8] Ming-Hsien Tsai, Shawn S. H. Hsu, Member, IEEE, Fu-Lung Hsueh, Chewn-Pu Jou, and Tzu-Jin Yeh "A 17.5–26 GHz Low-Noise Amplifier With Over 8 kV ESD Protection in 65 nm CMOS" 2012

- [9] Han-Chih Yeh, Student Member, IEEE, Ze-Yu Liao, Student Member, IEEE, and Huei Wang, Fellow, IEEE "Analysis and Design of Millimeter-Wave Low-Power CMOS LNA with Transformer-Multi cascade Topology" 2011.

- [10] Hsien-Ku Chen, Yo-Sheng Lin, Senior Member, IEEE, and Shey-Shi Lu, Senior Member, IEEE "Analysis and Design of a 1.6–28-GHz Compact Wideband LNA in 90-nm CMOS Using a -Match Input Network" 2010

- [11] Mingqi Chen, Student Member, IEEE, and Jenshan Lin, Senior Member, IEEE "A 0.1–20 GHz Low-Power Self-Biased Resistive-Feedback LNA in 90 nm Digital CMOS" 2009

- [12] Xiaohua Fan, Member, IEEE, Heng Zhang, Student Member, IEEE, and Edgar Sánchez-Sinencio, Fellow, IEEE "A Noise Reduction and Linearity Improvement Technique for a Differential Cascode LNA" 2008

- [13] Yueh-Hua Yu, Yi-Jan Emery Chen, Member, IEEE, and Deukhyoun Heo, Member, IEEE "A 0.6-V Low Power UWB CMOS LNA" 2007

- [14] Antonio Liscidini, Member, IEEE, Massimo Brandolini, Member, IEEE, Davide Sanzogni, Student Member, IEEE, and Rinaldo Castello, Fellow, IEEE "A 0.13 mm CMOS Front-End, for DCS1800/UMTS/ 802.11b-g With Multiband Positive Feedback Low-Noise Amplifier" 2006

- [15] Dimitri Linten, Student Member, IEEE, Steven Thijs, Mahadeva Iyer Natarajan, Senior Member, IEEE, Piet Wambacq, Member, IEEE, Wutthinan Jeamsaksiri, Member, IEEE, Javier Ramos, Abdelkarim Mercha, Member, IEEE, Snezana Jenei, Member, IEEE, Stéphane Donnay, Member, IEEE, and Stefaan Decoutere "A 5-GHz Fully Integrated ESD-Protected Low-Noise Amplifier in 90-nm RF CMOS" 2005.